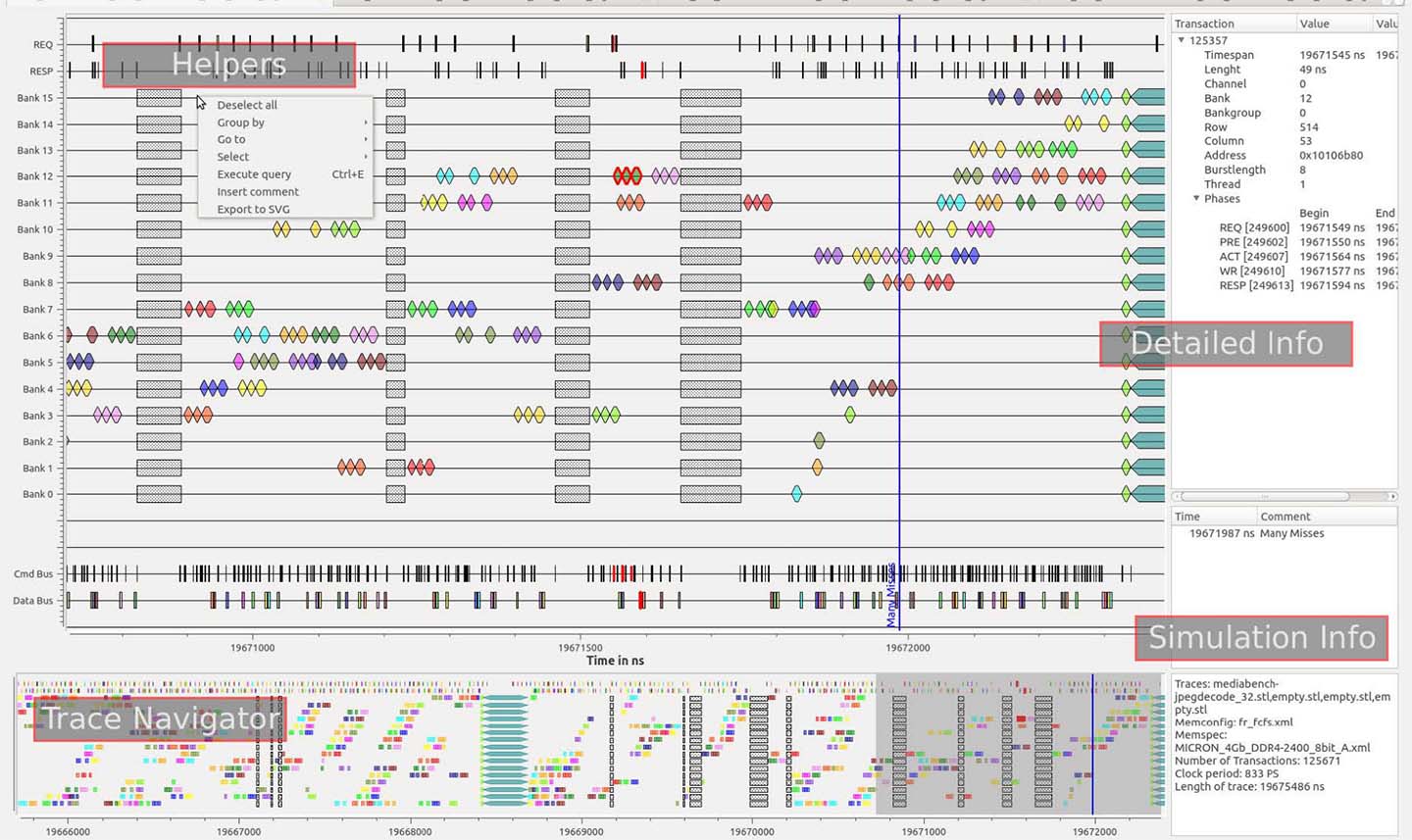

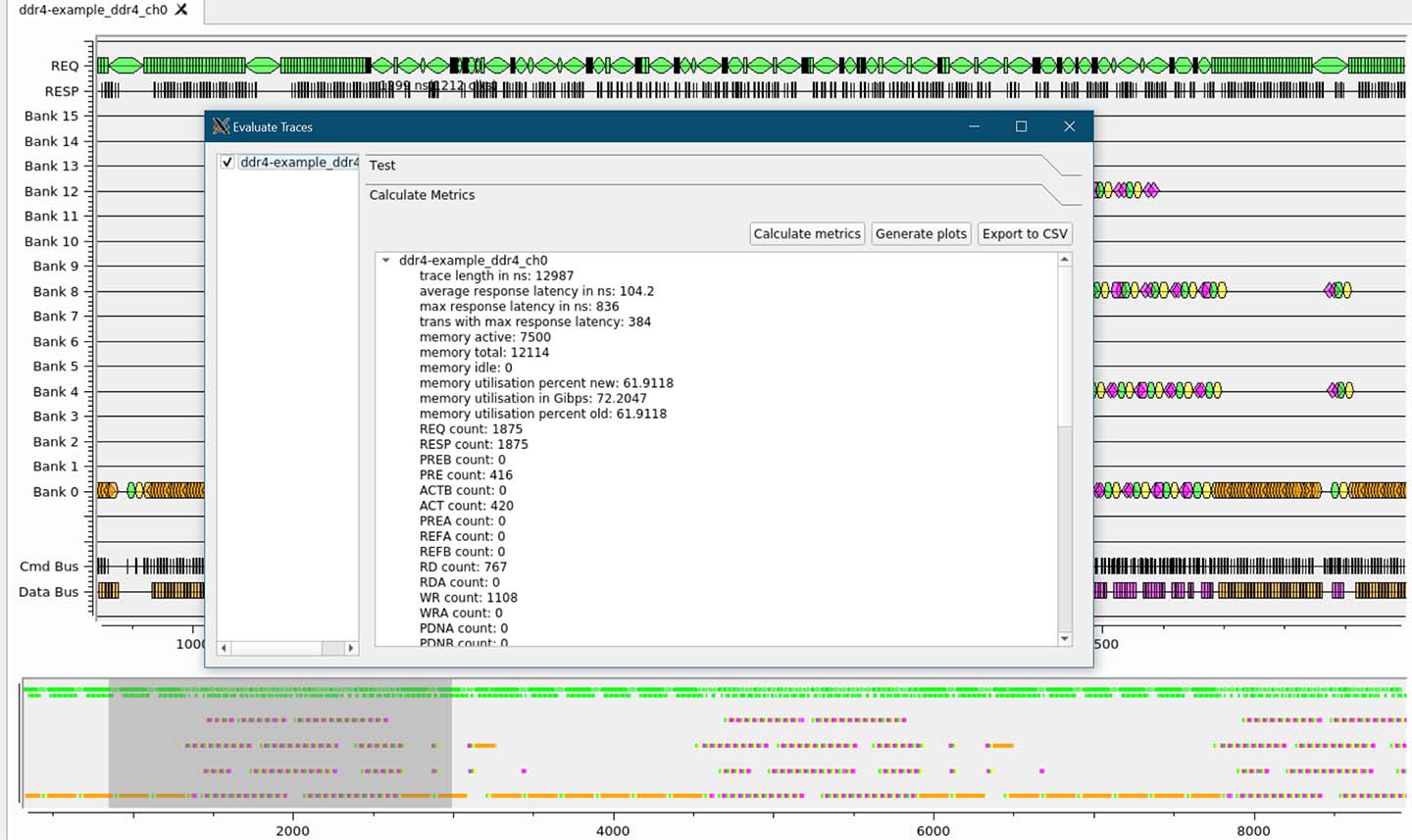

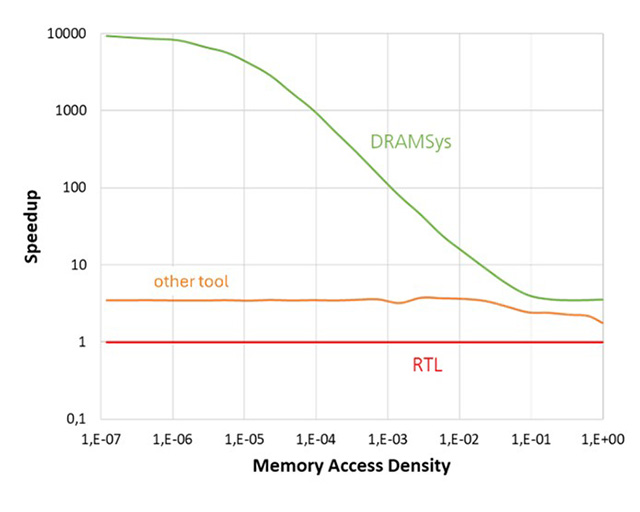

DRAMSys is the essential tool for developers and engineers who need full visibility into their product development with integrated DRAM subsystems. This advanced Open Source simulation framework is based on the SystemC TLM-2.0 standard and offers unprecedented flexibility and speed.

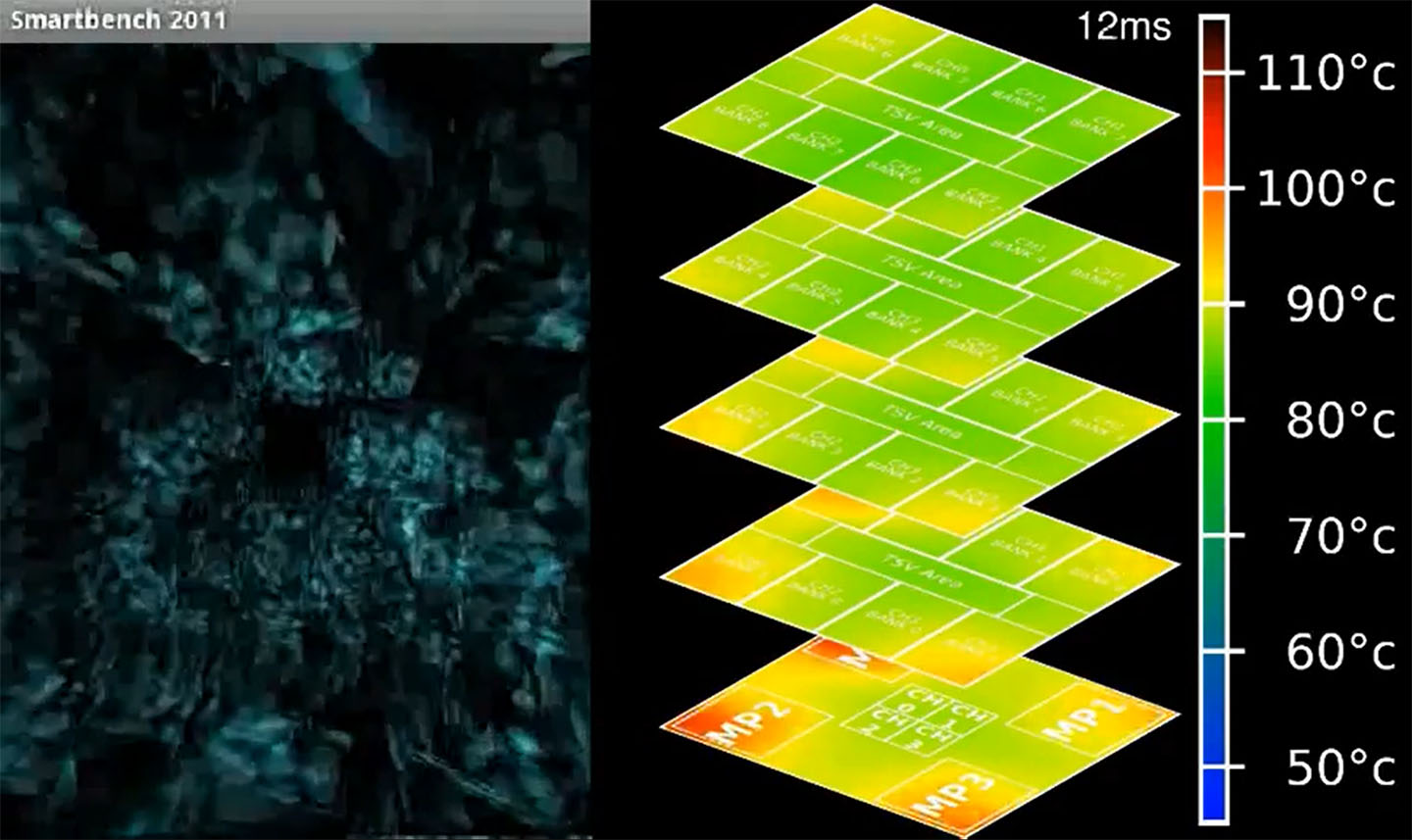

With DRAMSys you can easily master the challenges of modern memory systems. From analyzing power consumption to examining temperature distributions to identifying and correcting retention errors - DRAMSys offers you the options to optimally design your system.