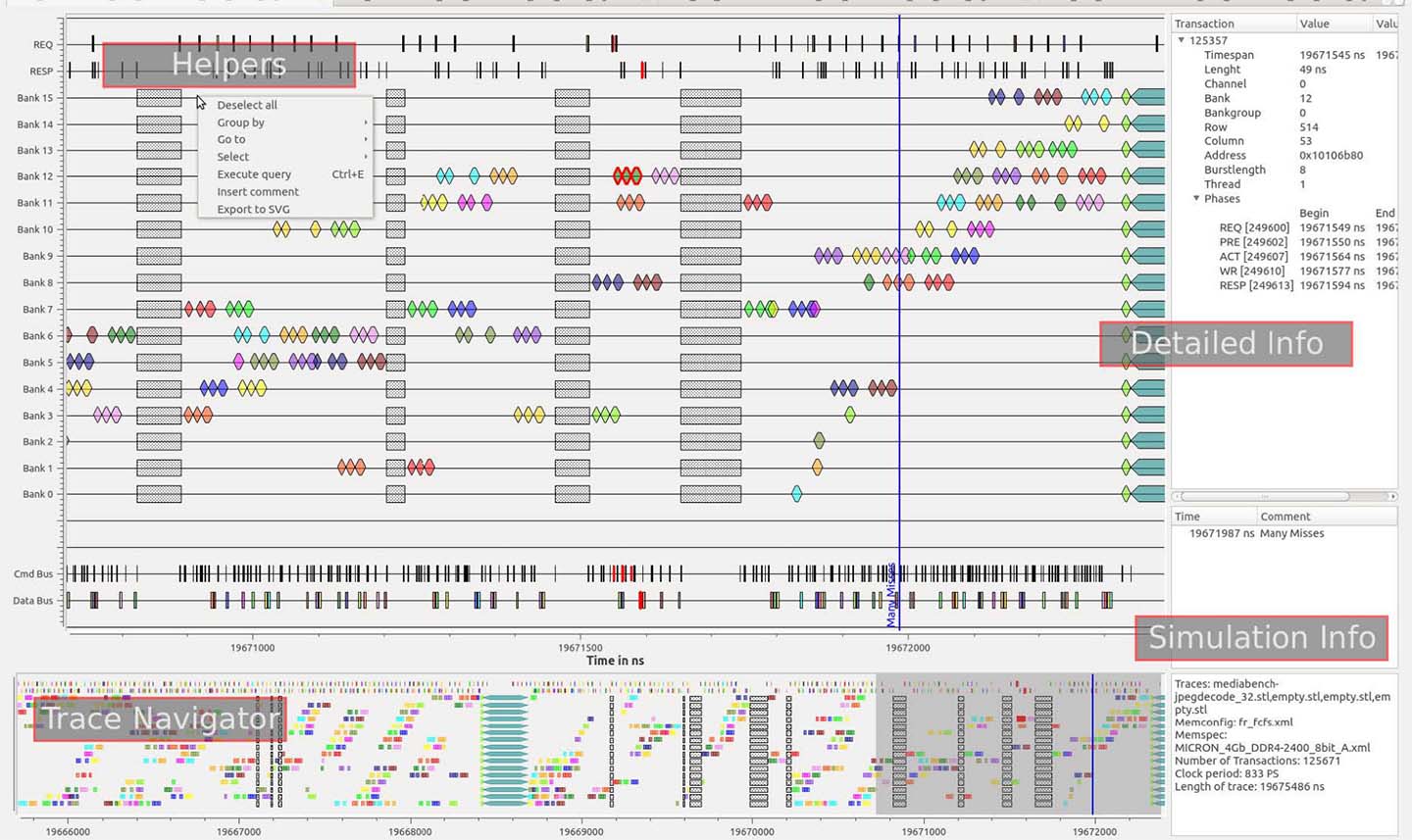

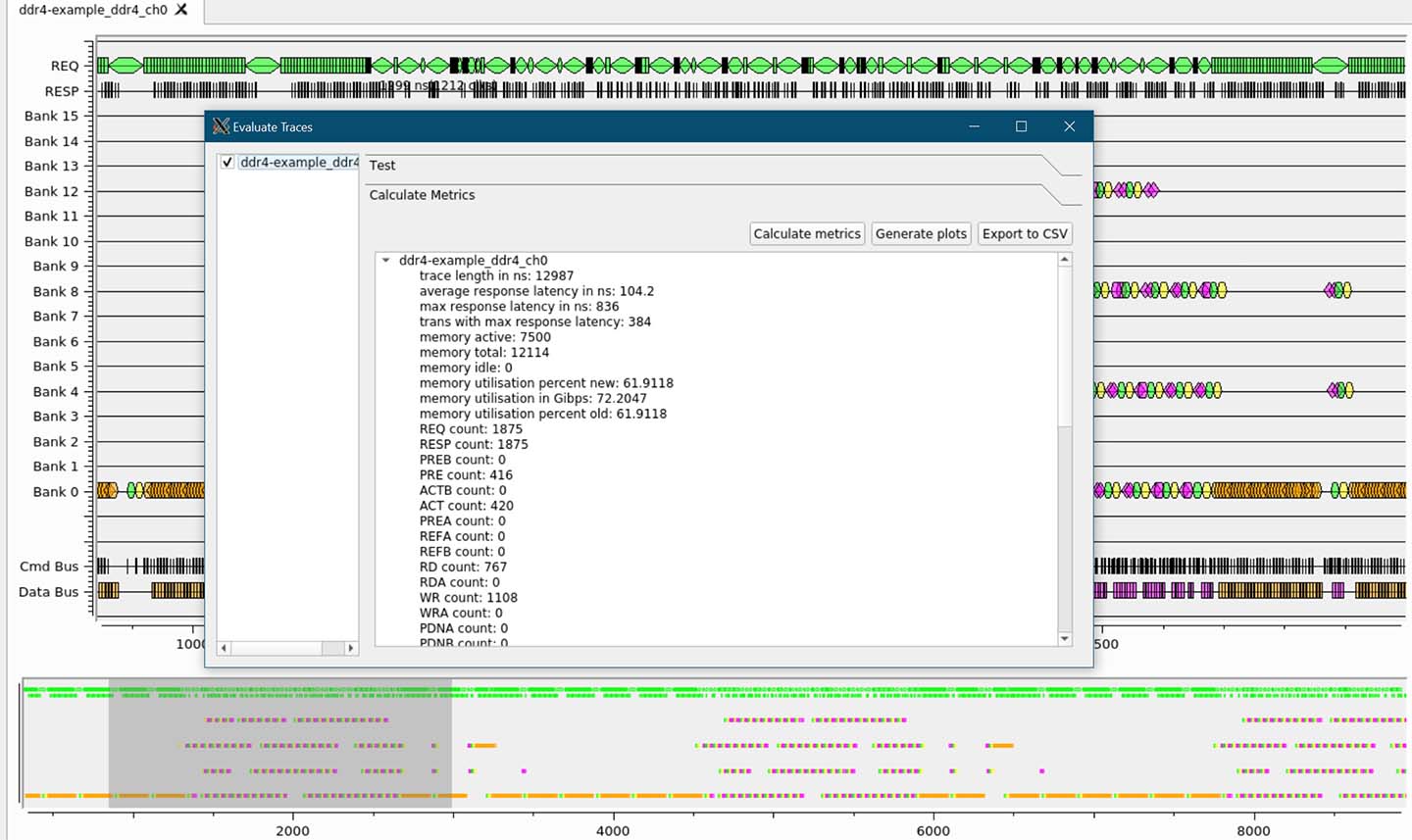

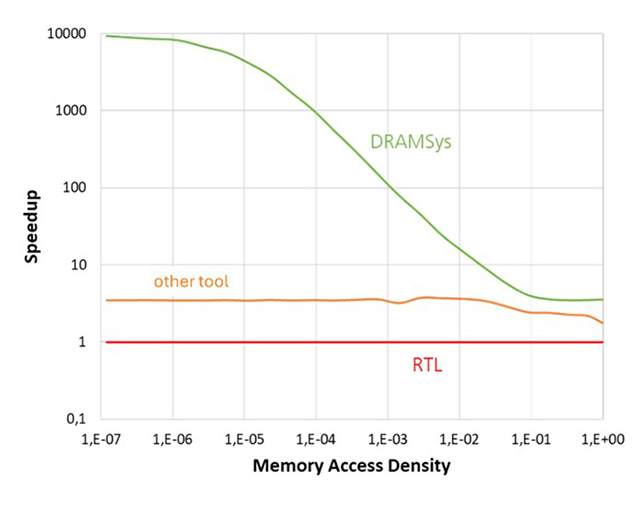

DRAMSys ist das unverzichtbare Tool für Entwickler und Ingenieure, die den vollen Überblick über ihre Produktentwicklung mit integrierten DRAM-Subsystemen benötigen. Dieses fortschrittliche Open-Source Simulations-Framework basiert auf dem SystemC TLM-2.0 Standard und bietet beispiellose Flexibilität und Geschwindigkeit.

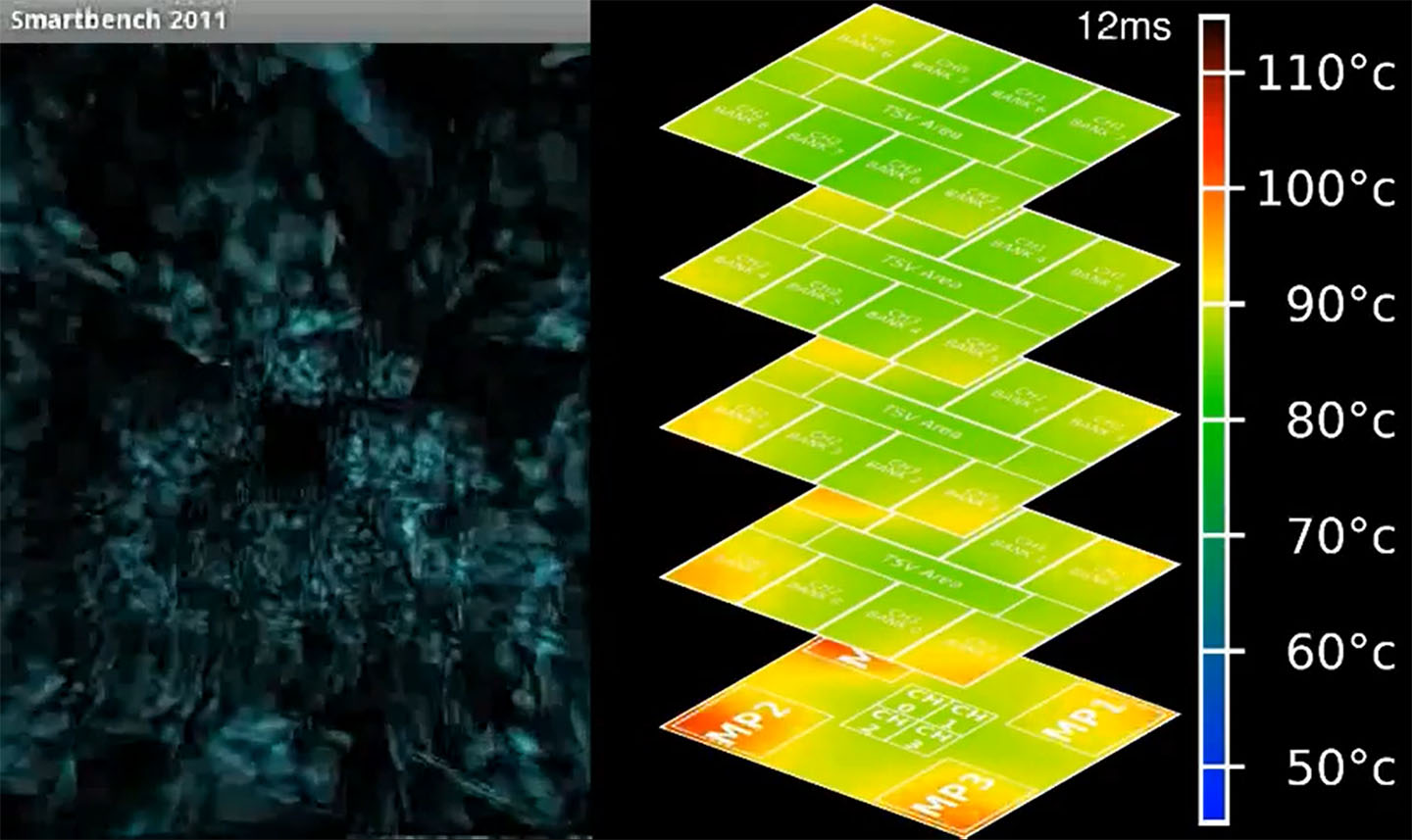

Mit DRAMSys können Sie die Herausforderungen moderner Speichersysteme spielend meistern. Von der Analyse der Leistungsaufnahme über die Untersuchung von Temperaturverteilungen bis hin zur Identifikation und Behebung von Retention-Fehlern – DRAMSys bietet Ihnen die Möglichkeiten, um Ihr System optimal zu gestalten.